# Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tirunelveli - 627 012 Tamilnadu, India

# **OPEN AND DISTANCE LEARNING (ODL) PROGRAMMES**

(FOR THOSE WHO JOINED THE PROGRAMMES FROM THE ACADEMIC YEAR 2023-2024)

II YEAR

# **M.Sc.** Physics

# **Course Material**

# **Microprocessor 8085 and Microcontroller 8051**

Prepared

Ву

Dr. S. Shailajha Assistant Professor Department of Physics Manonmaniam Sundaranar University Tirunelveli – 12

# UNIT I 8085 PROGRAMMING, PERIPHERAL DEVICES AND THEIR INTERFACING

Instruction set – Addressing Modes – Programming techniques – Memory mapped I/O scheme – I/O mapped I/O scheme – memory and I/O Interfacing – Data Transfer schemes – Interrupts of 8085 – Programmable peripheral Interface (PPI)- Control group and control word-Programmable DMA controller – Programmable Interrupt controller-Programmable communication Interface- Programmable counter/Interval timer.

### UNIT – II 8085 INTERFACING APPLICATIONS

Seven segment display Interface – Interfacing of Digital to Analog converter and Analog to Digital Converter – Stepper motor Interface – Measurement of electrical quantities – voltage and current), Measurement of Physical quantities (Temperature and Strain).

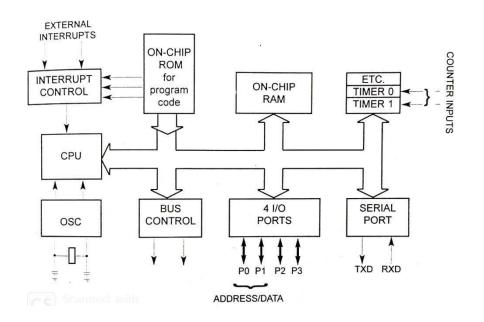

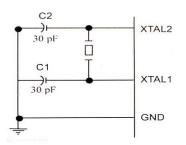

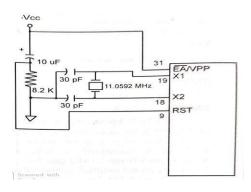

### UNIT-III 8051 MICROCONTROLLER HARDWARE

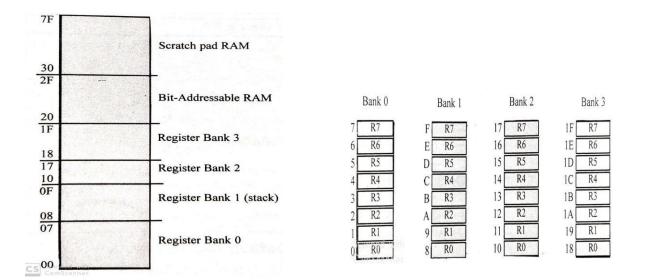

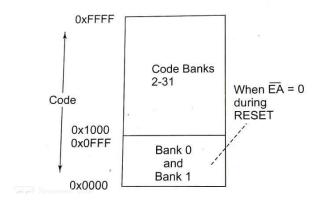

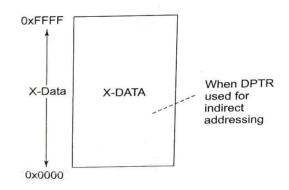

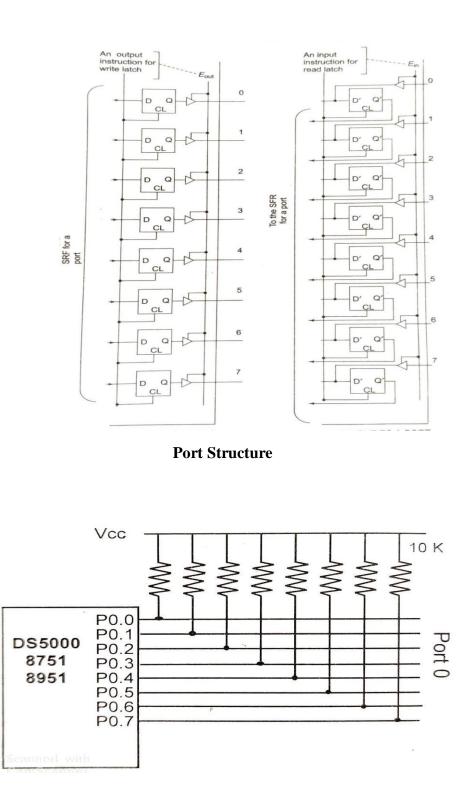

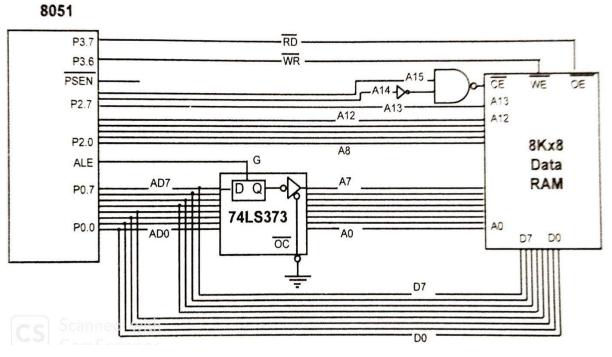

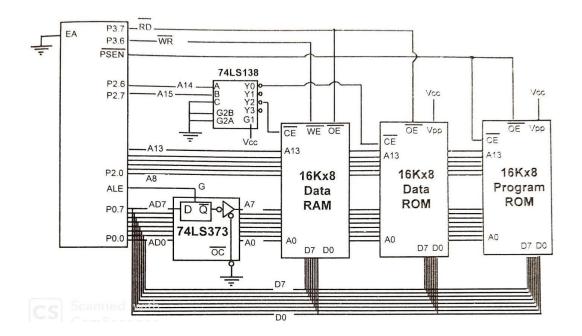

Introduction-Features of 8051-8051 Microcontroller Hardware pin -Out 8051, Central Processing Unit (CPU), Internal RAM, Internal ROM, Register set of 8051- Memory organization of 8051-Input/Output pins, Ports and Circuits-External data memory and Program memory: External Program Memory, External data memory.

## UNIT-IV 8051 INSTRUCTION SET AND ASSEMBLY LANGUAGE PROGRAMMING

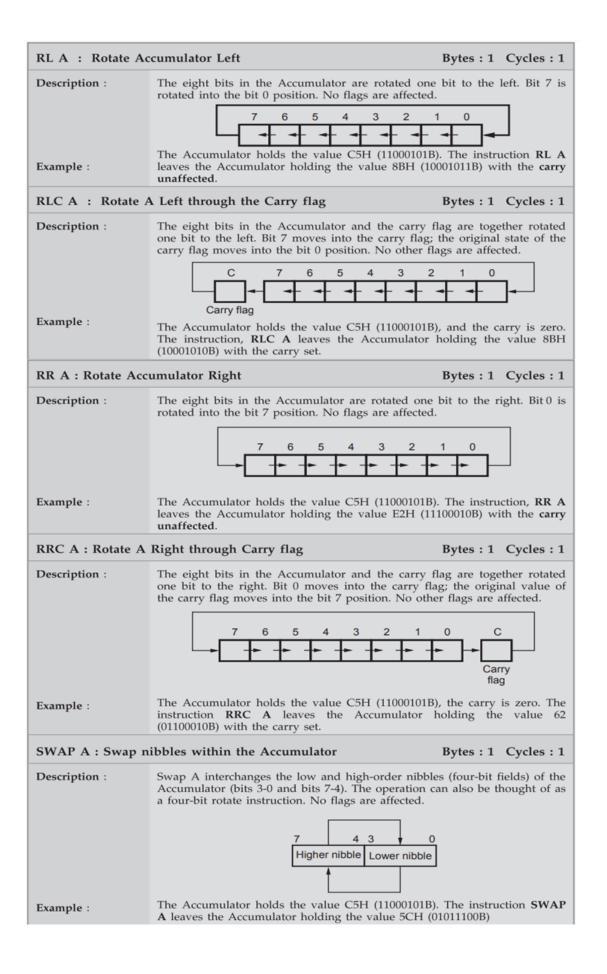

Addressing Modes-Data moving (data Transfer) Instructions: Instructions to Access external data memory, external ROM/Program memory, PUSH and POP instructions, Data exchange Instructions- Logical Instructions byte and bit level logical operations, Rotate and swap operations – Arithmetic instructions, Flags, Incrementing and decrementing, Addition, Subtraction, Multiplication and Division, Decimal Arithmetic – JUMP and CALL Instructions Jump and Call Program range, Jump, Call and subroutines – Programming.

#### UNIT -V

#### INTERUPPT PROGRAMMING AND INTERFACING TO EXTERNAL WORLD

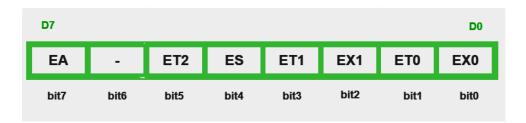

8051 Interrupts-Interrupt vector table-Enabling an disabling an interrupt – Timer Interrupts and Programming – Programming external hardware interrupts – serial communication interrupts and programming – Interrupt priority in the 8051: Nested interrupts, software trigerring of interrupt.LED interface seven segment display Interface – Interfacing of Digital to Analog converter and Analog to Digital Convertor – Stepper motor Interface- Measurement of electrical quantities – voltage and current), Measurement of Physical quantities (Temperature and Strain).

## UNIT VI PROFESSIONAL COMPONENTS

Expert Lectures, Online Seminars-Webinars on Industrial Interactions/Visits, Competitive Examinations, Employable and Communication Skill Enhancement, Social Accountability and Patriotism.

#### **TEXT BOOKS**

A. NAgoorkani, Microprocessors & Microcontrollers, RBA Publications (2009)

A.P.Godse and D.A.Godse, Microprocessors, Technical Publications, Pune (2009)

Ramesh Gaonkar, Microprocessor Architecture, Programming and 98 Applications with 8085, Penram International Publishing (2013)

B.Ram, Fundamentals of Microprocessors & Microcontrollers, DhanpatRai Publications New Delhi(2016) V.Vijayendran, 2005, Fundamentals of Microprocessor – 8085, 3<sup>rd</sup> Edition S. Visvanathan Pvt.Ltd.

# Unit 1 - 8085 Programming, Peripheral Devices and their Interfacing

## **INTRODUCTION**

#### Microcomputer:

The term microcomputer is generally synonymous with personal computer, or a computer that depends on a microprocessor.

• Microcomputers are designed to be used by individuals, whether in the form of PCs, workstations or notebook computers.

• A microcomputer contains a CPU on a microchip (the microprocessor), a memory system (typically ROM and RAM), a bus system and I/O ports, typically housed in a motherboard.

#### **Microprocessor:**

A silicon chip that contains a CPU. In the world of personal computers, the terms microprocessor and CPU are used interchangeably.

- A microprocessor (sometimes abbreviated µP) is a digital electronic component with miniaturized transistors on a single semiconductor integrated circuit (IC).

- One or more microprocessors typically serve as a central processing unit (CPU) in a computer system or handheld device.

- Microprocessors made possible the advent of the microcomputer.

- At the heart of all personal computers and most working stations sits a microprocessor.

- Microprocessors also control the logic of almost all digital devices, from clock radios to fuelinjection systems for automobiles.

- Three basic characteristics differentiate microprocessors:

- Instruction set: The set of instructions that the microprocessor can execute.

- Bandwidth: The number of bits processed in a single instruction.

- Clock speed: Given in megahertz (MHz), the clock speed determines how many instructions per second the processor can execute.

- In both cases, the higher the value, the more powerful the CPU. For example, a 32-bit microprocessor that runs at 50MHz is more powerful than a 16-bit microprocessor that runs at 25MHz.

In addition to bandwidth and clock speed, microprocessors are classified as being either RISC (reduced instruction set computer) or CISC (complex instruction set computer).

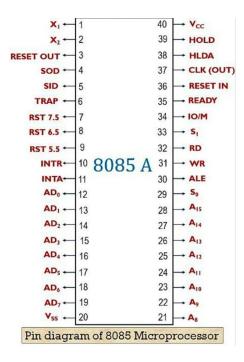

#### 8085 Microprocessor:

The Intel 8085 is an 8-bit microprocessor introduced by Intel in 1977. It was binary compatible with the more-famous Intel 8080 but required less supporting hardware, thus allowing simpler and less expensive microcomputer systems to be built. The "5" in the model number came from the fact that the 8085 requires only a +5-Volt (V) power supply rather than the +5 V, -5 V and +12 V supplies the 8080 needed. The main features of 8085  $\mu$ P are:

- It is an 8-bit microprocessor.

- It is manufactured with N-MOS technology.

- It has 16-bit address bus and hence can address up to 216=65536 bytes (64KB) memory locations through A<sub>0</sub>-A<sub>15</sub>.

- The first 8 lines of address bus and 8 lines of data bus are multiplexed AD<sub>0</sub>-AD<sub>7</sub>

- Data bus is a group of 8 lines  $D_0-D_7$ .

- It supports external interrupt request.

- A 16-bit program counter (PC)

- A 16-bit stack pointer (SP)

- Six 8-bit general purpose register arranged in pairs: BC, DE, HL.

- It requires a signal +5V power supply and operates at 3.2 MHZ single phase clock.

- It is enclosed with 40 pins DIP (Dual in line package).

**Instruction sets are instruction codes to perform some tasks. It is classified into five categories. Data Transfer Instructions:** Includes the instructions that moves (copies) data between registers or between memory locations and registers. In all data transfer operations, the content of source register is not altered. Hence the data transfer is copying operation.

**Arithmetic Instructions:** Includes the instructions, which performs the addition, subtraction, increment or decrement operations. The flag conditions are altered after execution of an instruction in this group.

**Logical Instructions:** The instructions which performs the logical operations like AND, OR, EXCLUSIVE-OR, complement, compare and rotate instructions are grouped under this heading. The flag conditions are altered after execution of an instruction in this group.

**Branching Instructions:** The instructions that are used to transfer the program control from one memory location to another memory location are grouped under this heading.

Machine Control Instructions: Includes the instructions related to interrupts and the instruction used to halt program execution.

# **Data Transfer Instructions**

- These instructions move data between registers, or between memory and registers.

- These instructions copy data from source to destination.

- While copying, the contents of source are not modified.

| Opcode | Operand                | Description                      |

|--------|------------------------|----------------------------------|

| MOV    | Rd, Rs M, Rs           | Copy from source to destination. |

|        | Rd, M                  |                                  |

|        |                        |                                  |

| MVI    | Rd, Data               | Move immediate 8-bit             |

|        | M, Data                |                                  |

| LDA    | 16-bit address         | Load Accumulator                 |

| LDAX   | B/D Register Pair      | Load accumulator indirect        |

| LXI    | Reg. pair, 16-bit data | Load register pair immediate     |

| STA    | 16-bit address         | Store accumulator direct         |

| STAX   | Reg. pair              | Store accumulator indirect       |

| XCHG   | None                   | Exchange H-L with D-E            |

### **Arithmetic Instructions**

These instructions perform arithmetic operations such as addition, s u b t r a c t i o n, increment, and decrement.

| Opcode | Operand    | Description                                      |

|--------|------------|--------------------------------------------------|

| ADD    | R          | Add register or memory to accumulator            |

|        | М          |                                                  |

| ADC    | R          | Add register or memory to accumulator with carry |

|        | М          |                                                  |

| ADI    | 8-bit data | Add immediate to accumulator                     |

| ACI    | 8-bit data | Add immediate to accumulator with carry          |

| SUB    | R          | Subtract register or memory from accumulator     |

|        | М          |                                                  |

| SUI    | 8-bit data | Subtract immediate from accumulator              |

| INR    | R          | Increment register or memory by 1                |

|        | М          |                                                  |

| INX    | R          | Increment register pair by 1                     |

| DCR    | R          | Decrement register or memory by 1                |

|        | М          |                                                  |

| DCX    | R          | Decrement register pair by 1                     |

## **Logical Instructions**

These instructions perform various logical operations with the contents of the accumulator

| Opcode | Operand    | Description                                      |  |

|--------|------------|--------------------------------------------------|--|

| CMP    | R          | Compare register or memory with accumulator      |  |

|        | М          |                                                  |  |

| CMP    | R          | Compare register or memory with accumulator      |  |

|        | М          |                                                  |  |

| CPI    | 8-bit data | Compare immediate with accumulator               |  |

| ANA    | R          | Logical AND register or memory with accumulator  |  |

|        | М          |                                                  |  |

| ANI    | 8-bit data | Logical AND immediate with accumulator           |  |

| XRA    | R          | Exclusive OR register or memory with accumulator |  |

|        | М          |                                                  |  |

| ORA    | R          | Logical OR register or memory with accumulator   |  |

|        | М          |                                                  |  |

| ORI    | 8-bit data | Logical OR immediate with accumulator            |  |

| XRA    | R          | Logical XOR register or memory with accumulator  |  |

|        | М          |                                                  |  |

| XRI    | 8-bit data | XOR immediate with accumulator                   |  |

# **Branching Instructions**

This group of instructions alters the sequence of program execution either conditionally or unconditionally.

| Opcode | Operand                           | perand Description |  |  |

|--------|-----------------------------------|--------------------|--|--|

| JMP    | JMP 16-bit address Jump unconditi |                    |  |  |

| Jx     | 16-bit address                    | Jump conditionally |  |  |

## **Machine Control Instructions**

These instructions control machine functions such as Halt, Interrupt, or do nothing.

| Opcode   | Operand | Description  |  |

|----------|---------|--------------|--|

| HLT      | None    | Halt         |  |

| NOP None |         | No operation |  |

| EI  | None | The interrupt enable flip-flop is set and all interrupts are<br>enabled. No flags are affected.                        |

|-----|------|------------------------------------------------------------------------------------------------------------------------|

| DI  | None | The interrupt enable flip-flop is reset and all the interrupts except the TRAP are disabled. No flags are affected.    |

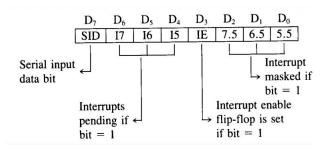

| SIM | None | This is a multipurpose instruction and used to implement the 8085 interrupts 7.5, 6.5, 5.5, and serial data output.    |

| RIM | None | This is a multipurpose instruction used to read the status of interrupts 7.5, 6.5, 5.5 and read serial data input bit. |

## **SIM Instruction**

# **RIM Instruction**

# **Addressing Modes**

Every instruction of a program has to operate on a data. The method of specifying the data to be operated by the instruction is called Addressing. The 8085 has the following 5 different types of addressing.

- Immediate Addressing

- Direct Addressing

- Register Addressing

- Register Indirect Addressing

- Implied Addressing

# **Immediate Addressing**

In immediate addressing mode, the data is specified in the instruction itself. The data will be a part of the program instruction.

EX. MVI B, 3EH - Move the data 3EH given in the instruction to B register; LXI SP, 2700H.

## **Direct Addressing**

In direct addressing mode, the address of the data is specified in the instruction. The data will be in memory. In this addressing mode, the program instructions and data can be stored in different memory.

**EX.** LDA 1050H - Load the data available in memory location 1050H in to accumulator; SHLD 3000H

# **Register Addressing**

In register addressing mode, the instruction specifies the name of the register in which the data is available.

EX. MOV A, B - Move the content of B register to A register; SPHL; ADD C.

# **Register Indirect Addressing**

In register indirect addressing mode, the instruction specifies the name of the register in which the address of the data is available. Here the data will be in memory and the address will be in the register pair.

EX. MOV A, M - The memory data addressed by H L pair is moved to A register. LDAX B.

# **Implied Addressing**

In implied addressing mode, the instruction itself specifies the data to be operated. EX. CMA -Complement the content of accumulator; RAL

# Programming techniques Memory Mapped I/O

There are two ways to interface 8085 with I/O devices in parallel data transfer mode:

- Memory Mapped IO

- IO Mapped IO

I/O devices are interfaced using address from memory space. That means IO device address are part of addresses given to memory locations.8085 uses 16-bit address to memory interfacing. So, any address between 0000H-FFFFH can be given to each peripheral. But the addresses given to peripheral can't be used for memory. Memory control signals are used as read and write control signals for peripherals. And all the operations that can be performed on memory can also be performed on peripherals. No need of using IO instructions such as IN, OUT.

## IO mapped I/O

In this method separate address space is given to IO devices. Each IO device is given an 8-bit address. Hence maximum 256 devices can be interfaced to the processor. The address range for the IO devices is 00H-FFH. IO control signals are used to perform read, write operations. For reading data from IO device or writing data to IO device IN, OUT instructions need to be used.

| Memory Mapped IO                                          | IO mapped IO                                                 |

|-----------------------------------------------------------|--------------------------------------------------------------|

| IO is treated as memory.                                  | IO is treated IO.                                            |

| 16-bit addressing.                                        | 8- bit addressing.                                           |

| More Decoder Hardware.                                    | Less Decoder Hardware.                                       |

| Can address 2 <sup>16</sup> =64k locations.               | Can address $2^8 = 256$ locations.                           |

| Less memory is available.                                 | Whole memory address space is available.                     |

| Memory Instructions are used.                             | Special Instructions are used like IN, OUT.                  |

| Memory control signals are used.                          | Special control signals are used.                            |

| Arithmetic and logic operations can be performed on data. | Arithmetic and logic operations cannot be performed on data. |

| Data transfer b/w register and IO.                        | Data transfer b/w accumulator and IO.                        |

# **IO mapped IO vs. Memory Mapped IO**

Arithmetic and logical operations can't be performed directly on IO devices as in memory mapped IO. IO devices can be interfaced, by using buffers for simple IO i.e. by using address decoding circuit to enable buffer. For handshake IO or to interface more peripherals ICs like 8255 peripheral programmable interfaces (PPI) can be used.

# **Memory Interfacing**

The following are the steps involved in interfacing memory with 8085 processor.

1. First decide the size of memory requires to be interfaced. Depending on this we can say how many address lines are required for it. For example, if you want to interface 4KB (2<sup>12</sup>) memory it requires 12 address lines. Remaining address lines can be used in address decoding.

2. Depending on the size of memory required and given address range, construct address decoding circuitry. This address decoding circuitry

can be implemented with NAND gates and/or decoders or using PAL (when board size is a constraint).

3. Connect data bus of memory to processor data bus.

4. Generate the control signals required for memory using IO/M', WR', RD' signals of 8085 processor.

## **Interfacing I/O Devices**

- 1. Using I/O devices data can be transferred between the microprocessor and the outside world.

- 2. This can be done in groups of 8 bits using the entire data bus. This is called parallel I/O.

- 3. The other method is serial I/O where one bit is transferred at a time using the SID and SOD pins on the Microprocessor.

#### The interfacing of output devices

Output devices are usually slow.

- Also, the output is usually expected to continue appearing on the output device for a long period of time.

- Given that the data will only be present on the data lines for a very short period (microseconds), it has to be latched externally.

- To do this the external latch should be enabled when the port's address is present on the address bus, the IO/M signal is set high and WR is set low.

- The resulting signal would be active when the output device is being accessed by the microprocessor.

- Decoding the address bus (for memory-mapped devices) follows the same techniques discussed in interfacing memory.

## **Interfacing of Input Devices**

- The basic concepts are similar to interfacing of output devices.

- The address lines are decoded to generate a signal that is active when the particular port is being accessed.

- An IORD signal is generated by combining the IO/M and the RD signals from the microprocessor.

- A tri-state buffer is used to connect the input device to the data bus.

- The control (Enable) for these buffers is connected to the result of combining the address signal and the signal IORD.

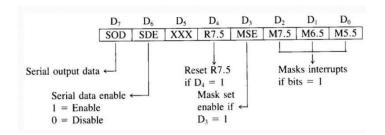

## Data transfer schemes

At the time of executing one 8085 program, interruption can be done in the mid-way by the virtue of the program by an Input Output device. Interruption can be done by the method according to which the processor works, since it wants urgent communication with the processor. The data transfer schemes always want for sending information to the processor, rather receiving information from the 8085 processor. It is so because sending and receiving information in the entire 8085 data transfer scheme process plays a vital role for executing the entire program rather process.

The communication is not done directly with the Input Output device. The communication processes are carried out systematically by the help of Input Output device by the virtue of an Input.

Output port. The data transfer can be either in two forms namely parallel or serial respectively. By the virtue of the Programmed Input Access or rather transferring data in parallel the data transfer

can be possible by using the Input Output programmed part or by Direct Memory Access (DMA) scheme. For transferring data in parallel we have three different ways by means of which microprocessor communicates with an Input or Output. They are:

**Basic or simple data transfer scheme:** The simplest data transfer scheme is the basic or simple data transfer. This method is beneficial to us when we have accurate know-ledge of the Input Output device timing characteristics.

**Status check data transfer:** Status check data transfer process is a much more complex process than simple data transfer. We use this method is used when there is lack of accurate knowledge of the Input Output device consisting of the timing characteristics. Status information is received by the processor regarding the readiness of the Input Output device for performing the data transfer.

**Interrupt driven data transfer:** We use this method when there lacks accurate knowledge of the timing characteristics of the Input Output device which takes maximum time for the device to be ready for use. Suppose we resort for the checking of data transfer; the processor here wastes a huge time in the loop for the device to get ready up to the mark.

#### Interrupt of 8085

Consider that a microprocessor is executing the main program. Now whenever the interrupt signal is enabled or requested the microprocessor shifts the control from main program to process the incoming request and after the completion of request, the control goes back to the main program. For example, an Input/output device may send an interrupt signal to notify that the data is ready for input. The microprocessor temporarily stops the execution of main program and transfers control to I/O device. After collecting the input data, the control is transferred back to main program. Interrupt signals present in 8085 are:

- INTR

- RST 7.5

- RST 6.5

- RST 5.5

- TRAP

INTR is maskable 8080A compatible interrupt. When the interrupt occurs the processor fetches from the bus one instruction, usually one of these instructions: One of the 8 RST instructions (RST0 - RST7). The processor saves current program counter into stack and branches to memory location N \* 8 (where N is a 3 - bit number from 0 to 7 supplied with the RST instruction).

CALL instruction (3-byte instruction). The processor calls the subroutine, address of which is specified in the second and third bytes of the

**RST5.5** is a maskable interrupt. When this interrupt is received the processor saves the contents of the PC register into stack and branches to 2CH (hexadecimal) address.

**RST6.5** is a maskable interrupt. When this interrupt is received the processor saves the contents of the PC register into stack and branches to 34H (hexadecimal) address.

**RST7.5** is a maskable interrupt. When this interrupt is received the processor saves the contents of the PC register into stack and branches to 3CH (hexadecimal) address.

**TRAP** is a non-maskable interrupt. When this interrupt is received the processor saves the contents of the PC register into stack and branches to 24H (hexadecimal) address.

All maskable interrupts can be enabled or disabled using EI and DI instructions. RST5.5, RST6.5 and RST7.5 interrupts can be enabled or disabled individually using SIM instruction.

**NON-VECTORED INTERRUPT:** The address of the service routine is not known in prior to the microprocessor. It is sent by the interrupting device. When the interrupt flipflop is enabled and INTR is high, microprocessor executes the current instruction and makes INTA low. Based on the flexibility to enable or disable interrupt, the interrupts are classified as maskable interrupt and non maskable interrupt. Maskable Interrupt: Even if the interrupt signals are high, microprocessor will respond to these signals only when interrupt flip flop is enabled. Example RST 7.5, RST 6.5, RST 5.5, INTR Non-Maskable Interrupt: Once the signal is enabled, the microprocessor immediately responds to this interrupt. Example: TRAP

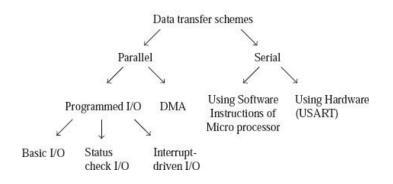

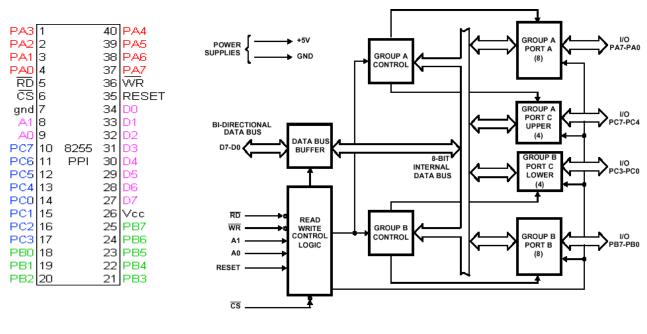

# **Programmable Peripheral Interface 8255**

The 8255 is a widely used, programmable, parallel I/O device. It can be programmed to transfer data under various conditions, from simple I/O to interrupt I/O. It is flexible, versatile and economical and complex.

# Features

Three 8-bit IO ports PA, PB, PC

- PA can be set for Modes 0, 1, 2. PB for 0,1 and PC for mode 0 and for BSR. Modes 1 and 2 are interrupt driven.

- PC has 2 4-bit parts: PC upper (PCU) and PC lower (PCL), each can be set independently for I or O. Each PC bit can be set/reset individually in BSR mode.

- PA and PCU are Group A (GA) and PB and PCL are Group B (GB)

- Address/data bus must be externally demultiplexed.

- TTL compatible.

- Improved dc driving capability

8255 Pin Diagram

8255 Block Diagram

**Data Bus Buffer:** This three-state bi-directional 8-bit buffer is used to interface the 8255 to the system data bus. Data is transmitted or received by the buffer upon execution of input or output instructions by the CPU. Control words and status information are also transferred through the data bus buffer.

**Read/Write and Control Logic:** The function of this block is to manage all of the internal and external transfers of both Data and Control or Status words. It accepts inputs from the CPU Address and Control busses and in turn, issues commands to both of the Control Groups.

(CS) Chip Select. A "low" on this input pin enables the communication between the 8255 and the CPU.

(**RD**) **Read:** A "low" on this input pin enables 8255 to send the data or status information to the CPU on the data bus. In essence, it allows the CPU to "read from" the 8255.

(WR) Write: A "low" on this input pin enables the CPU to write data or control words into the 8255.

(A0 and A1) Port Select 0 and Port Select 1: These input signals, in conjunction with the RD and WR inputs, control the selection of one of the three ports or the control word register. They are normally connected to the least significant bits of the address bus (A0 and A1).

(**RESET**) **Reset.** A "high" on this input initializes the control register to 9Bh and all ports (A, B, C) are set to the input mode.

| A1 | A0 | Selection |

|----|----|-----------|

| 0  | 0  | Port A    |

| 0  | 1  | Port B    |

| 1  | 0  | Port C    |

| 1  | 1  | Control   |

# Group A and Group B Controls

The functional configuration of each port is programmed by the systems software. In essence, the CPU "outputs" a control word to the 8255. The control word contains information such as "mode", "bit set", "bit reset", etc., that initializes the functional configuration of the 8255. Each of the Control blocks (Group A and Group B) accepts "commands" from the Read/Write Control logic, receives "control words" from the internal data bus and issues the proper commands to its associated ports.

# Ports A, B, and C

The 8255 contains three 8-bit ports (A, B, and C). All can be configured to a wide variety of functional characteristics by the system software but each has its own special features or "personality" to further enhance the power and flexibility of the 8255.

Port A One 8-bit data output latch/buffer and one 8-bit data input latch. Both "pull-up" and "pulldown" bus-hold devices are present on Port A.

Port B One 8-bit data input/output latch/buffer and one 8-bit data input buffer.

Port C One 8-bit data output latch/buffer and one 8-bit data input buffer (no latch for input).

This port can be divided into two 4-bit ports under the mode control. Each 4-bit port contains a 4-bit latch and it can be used for the control signal output and status signal inputs in conjunction with ports A and B.

## **Operational modes of 8255**

There are two basic operational modes of 8255:

- Bit set/reset Mode (BSR Mode).

- Input/output Mode (I/O Mode).

The two modes are selected on the basis of the value present at the D7 bit of the Control Word Register. When D7 = 1, 8255 operates in I/O mode and when D7 = 0, it operates in the BSR mode.

#### Bit set/reset (BSR) mode

The Bit Set/Reset (BSR) mode is applicable to port C only. Each line of port C (PC0 - PC7) can be set/reset by suitably loading the control word register. BSR mode and I/O mode are independent and selection of BSR mode does not affect the operation of other ports in I/O mode.

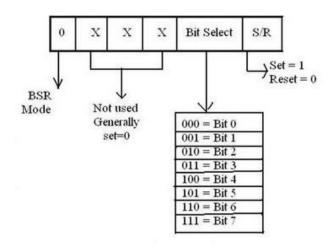

control word BSR mode

D<sub>7</sub> bit is always 0 for BSR mode.

Bits D<sub>6</sub>, D<sub>5</sub> and D<sub>4</sub> are don't care bits.

Bits D<sub>3</sub>, D<sub>2</sub> and D<sub>1</sub> are used to select the pin of Port C.

Bit  $D_0$  is used to set/reset the selected pin of Port C.

Selection of port C pin is determined as follows

| <b>B3</b> | <b>B2</b> | <b>B1</b> | Bit/pin of port C |

|-----------|-----------|-----------|-------------------|

|           |           |           | selected          |

| 0         | 0         | 0         | PC0               |

| 0         | 0         | 1         | PC1               |

| 0         | 1         | 0         | PC2               |

| 0         | 1         | 1         | PC3               |

| 1         | 0         | 0         | PC4               |

| 1         | 0         | 1         | PC5               |

| 1         | 1         | 0         | PC6               |

| 1         | 1         | 1         | PC7               |

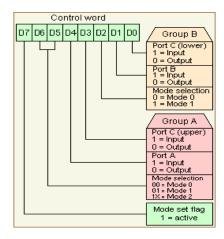

### Input/Output mode

This mode is selected when D7 bit of the Control Word Register is 1. There are three I/O modes:

Mode 0 - Simple I/O

Mode 1 - Strobed I/O

Mode 2 - Strobed Bi-directional I/O

$D_0$ ,  $D_1$ ,  $D_3$ ,  $D_4$  are assigned for lower port C, port B, upper port C and port A respectively. When these bits are 1, the corresponding port acts as an input port. For e.g., if  $D_0 = D_4 = 1$ , then lower port C and port A act as input ports. If these bits are 0, then the corresponding port acts as an output port. For e.g., if  $D_1 = D_3 = 0$ , then port B and upper port C act as output ports.  $D_2$  is used for mode selection of Group B (port B and lower port C). When  $D_2 = 0$ , mode 0 is selected and when  $D_2 = 1$ , mode 1 is selected.

Control word I/O mode

$D_5 \& D_6$  are used for mode selection of Group A (port A and upper port C). The selection is done as follows:

| D6 | D5 | Mode |

|----|----|------|

| 0  | 0  | 0    |

| 0  | 1  | 1    |

| 1  | Х  | 2    |

As it is I/O mode,  $D_7 = 1$ .

#### Mode 0 - Simple I/O

In this mode, the ports can be used for simple I/O operations without handshaking signals. Port A, port B provide simple I/O operation. The two halves of port C can be either used together as an additional 8-bit port, or they can be used as individual 4-bit ports. Since the two halves of port C are

independent, they may be used such that one-half is initialized as an input port while the other half is initialized as an output port.

- The input/output features in mode 0 are as follows:

- Output ports are latched.

- Input ports are buffered, not latched.

- Ports do not have handshake or interrupt capability.

- With 4 ports, 16 different combinations of I/O are possible.

# Mode 0 – input mode

- In the input mode, the 8255 gets data from the external peripheral ports and the CPU reads the received data via its data bus.

- The CPU first selects the 8255 chip by making CS' low. It then selects the desired port using A0 and A1 lines.

- The CPU then issues an RD' signal to read the data from the external peripheral device via the system data bus.

# Mode 0 - Output mode

- In the output mode, the CPU sends data to 8255 via system data bus and then the external peripheral ports receive this data via 8255 port.

- CPU first selects the 8255 chip by making CS' low. It then selects the desired port using A0 and A1 lines.

- CPU then issues a WR' signal to write data to the selected port via the system data bus. This data is then received by the external peripheral device connected to the selected port.

## Mode 1

When we wish to use port A or port B for handshake (strobed) input or output operation, we initialise that port in mode 1 (port A and port B can be initialised to operate in different modes, i.e., for e.g., port A can operate in mode 0 and port B in mode 1). Some of the pins of port C function as handshake lines.

For port B in this mode (irrespective of whether is acting as an input port or output port), PC0, PC1 and PC2 pins function as handshake lines. If port A is initialised as mode 1 input port, then, PC3, PC4 and PC5 function as handshake signals. Pins PC6 and PC7 are available for use as input/output lines.

The mode 1 which supports handshaking has following features:

- Two ports i.e. port A and B can be used as 8-bit i/o ports.

- Each port uses three lines of port c as handshake signal and remaining two signals can be used as i/o ports.

- Interrupt logic is supported.

- Input and Output data are latched.

#### **Input Handshaking signals**

1. IBF (Input Buffer Full) - It is an output indicating that the input latch contains information.

2. STB (Strobed Input)-The strobe input loads data into the port latch, which holds the information until it is input to the microprocessor via the IN instruction.

3. INTR (Interrupt request)-It is an output that requests an interrupt. The INTR pin becomes a logic 1 when the STB input returns to a logic 1, and is cleared when the data are input from the port by the microprocessor.

4. INTE (Interrupt enable)-It is neither an input nor an output; it is an internal bit programmed via the port PC4(port A) or PC2(port B) bit position.

#### **Output Handshaking signals**

1. OBF (Output Buffer Full)-It is an output that goes low whenever data are output (OUT) to the port A or port B latch. This signal is set to a logic 1 whenever the ACK pulse returns from the external device.

2. ACK(Acknowledge)-It causes the OBF pin to return to a logic 1 level. The ACK signal is a response from an external device, indicating that it has received the data from the 82C55 port.

3. INTR (Interrupt request)-It is a signal that often interrupts the microprocessor when the

4. External device receives the data via the signal. this pin is qualified by the internal INTE (interrupt enable) bit.

5. INTE (Interrupt enable)-It is neither an input nor an output; it is an internal bit programmed to enable or disable the INTR pin. The INTE A bit is programmed using the PC6 bit and INTE B is programmed using the PC2 bit.

#### **DMA** Controller

#### DMA Signals: HOLD, HLDA, READY

• HOLD: Indicates that another master is requesting the use of the address and data buses. The CPU, upon receiving the hold request, will relinquish the use of the bus as soon as the completion of the current bus transfer. Internal processing can continue. The processor can

regain the bus only after the HOLD is removed. When the HOLD is acknowledged, the Address, Data RD, WR and IO/M' lines are tri-stated.

- HLDA: Hold Acknowledge: Indicates that the CPU has received the HOLD request and that it will relinquish the bus in the next clock cycle HLDA goes low after the Hold request is removed. The CPU takes the bus one half-clock cycle after HLDA goes low.

- **READY:** This signal synchronizes the fast CPU and the slow memory, peripherals. If READY is high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive data. If READY is low, the CPU will wait an integral number of clock cycle for READY to go high before completing the read or write cycle. READY must conform to specified setup and hold times.

# Reset Signals: Reset in, Reset Out

#### **RESET IN:** A low on this pin;

- Sets the program counter to zero (0000H)

- Resets the interrupt enables and HLDA flip-flops.

- Tri-states the data bus, address bus and control bus.

- Affects the content of processors internal registers randomly.

On Reset, The Program counter sets to 0000h which causes the 8085 to execute; the first instruction from address 0000H.

**RESET OUT:** This active high signal indicates that the processor; is being reset. This signal is synchronized to the processor clock and it can be used to reset other devices connected in the system.

## Serial Input/output control

The input and output of serial data can be carried out using 2 instructions in 8085.

- SID-Serial Input Data

- SOD-Serial Output Data

Two more instructions are used to perform serial-parallel conversion needed for serial I/O devices.

- SIM

- RIM

# Address buffer and Address-Data buffer

The contents of the stack pointer and program counter are loaded into the address buffer and addressdata buffer. These buffers are then used to drive the external address bus and address-data bus. As the memory and I/O chips are connected to these buses, the CPU can exchange desired data to the memory and I/O chips.

The address-data buffer is not only connected to the external data bus but also to the internal data bus which consists of 8-bits. The address data buffer can both send and receive data from internal data bus.

#### Address bus and Data bus

We know that 8085 is an 8-bit microprocessor. So, the data bus present in the microprocessor is also 8-bits wide. So, 8-bits of data can be transmitted from or to the microprocessor. But 8085 processor requires 16-bit address bus as the memory addresses are 16-bit wide. The 8 most significant bits of the address are transmitted with the help of address bus and the 8 least significant bits are transmitted with the help of multiplexed address/data bus. The eight- bit data bus is multiplexed with the eight

least significant bits of address bus. The address/data bus is time multiplexed. This means for few microseconds, the 8 least significant bits of address are generated, while for next few seconds the same pin generates the data. This is called Time multiplexing. But there are situations where there is a need to transmit both data and address simultaneously. For this purpose, a signal called ALE (address latch enables) is used. ALE signal holds the obtained address in its latch for a long time until the data is obtained and so when the microprocessor sends the data next time the address is also available at the output latch. This technique is called Address/Data demultiplexing.

#### **Programmable Interrupt Controller**

The Intel 8259A Programmable Interrupt Controller handles up to eight vectored priority interrupts for the CPU. It is cascadable for up to 64 vectored priority interrupts without additional circuitry. It is packaged in a 28-pin DIP, uses NMOS technology and requires a single a 5V supply. Circuitry is static, requiring no clock input. The 8259A is designed to minimize the software and real time overhead in handling multi-level priority interrupts. It has several modes, permitting optimization for a variety of system requirements. The PIC receives an interrupt request from an I/O device and tells the microprocessor. The CPU completes whatever instruction it is currently executing and then fetches a new routine that will service the requesting device. Once this peripheral service is completed, the CPU resumes doing exactly what it was doing when the interrupt request occurred. The PIC functions as an overall manager of hardware interrupt requests in an interrupt driven system environment.

# Features

- 8 levels of interrupts.

- Can be cascaded in master-slave configuration to handle 64 levels of interrupts.

- Internal priority resolver, Fixed priority mode and rotating priority mode.

- Individually maskable interrupts.

- Modes and masks can be changed dynamically.

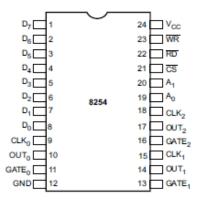

# **Programmable Interval Timer**

The 8253 solves one of most common problem in any microcomputer system, the generation of accurate time delays under software control. Instead of setting up timing loops in system software, the programmer configures the 8253 to match his requirements, initializes one of the counters of the 8253 with the desired quantity, then upon command the 8253 will count out the delay and interrupt the CPU when it has completed its tasks.

It is easy to see that the software overhead is minimum and that multiple delays can be easily be maintained by assignment of priority levels. The 8253 includes three identical 16-bit counters that can operate independently. To operate a counter, a 16-bit count is loaded in its register and, on command, it begins to decrement the count until it reaches 0. At the end of the count, it generates a pulse that can be used to interrupt the CPU. The counter can count either in binary or BCD. In addition, a count can be read by the CPU while the counter is decrementing.

## Features

- 1. Three independent 16-bit down counters.

- 2. 8253 can operate from DC up to 2.6 MHz

- Three counters are identical presettable, and can be programmed for either binary or BCD count.

- 4. Counter can be programmed in six different modes.

- 5. Compatible with all Intel and most other microprocessors.

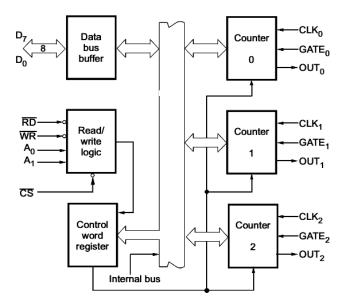

It includes three counters, a data bus buffer, Read/Write control logic, and a control register. Each counter has two input signals CLOCK and GATE and one output signal OUT.

#### **Pin Diagram**

8254 Block Diagram

**Data Bus Buffer:** This tri-state, bi-directional, 8-bit buffer is used to interface the 8253 to the system data bus. The Data bus buffer has three basic functions.

- 1. Programming the modes of 8253.

- 2. Loading the count registers.

- 3. Reading the count values.

**Read/Write Logic:** The Read/Write logic has five signals: RD, WR, CS and the address lines A0 and A1. In the peripheral I/O mode, the RD, and WR signals are connected to IOR and IOW, respectively. In memory-mapped I/O, these are connected to MEMR and MEMW. Address lines A0

and A1 of the CPU are usually connected to lines A0 and A1 of the 8253, and CS is tied to a decoded address. The control word register and counters are selected according to the signals on lines A0 and A1. It includes three counters, a data bus buffer, Read/Write control logic, and a control register. Each counter has two input signals CLOCK and GATE and one output signal OUT.

| A <sub>1</sub> | $\mathbf{A}_{0}$ | Selection             |  |  |

|----------------|------------------|-----------------------|--|--|

| 0              | 0                | Counter 0             |  |  |

| 0              | 1                | Counter 1             |  |  |

| 1              | 0                | Counter 2             |  |  |

| 1              | 1                | Control word Register |  |  |

**Control Word Register:** This register is accessed when lines  $A_0$  and  $A_1$  are at logic 1. It is used to write a command word which specifies the counter to be used (binary or BCD), its mode, and either a read or write operation.

**Counters:** These three functional blocks are identical in operation. Each counter consists of a single, 16-bit, pre-settable, down counter. The counter can operate in either binary or BCD and its input, gate and output are configured by the selection of modes stored in the control word register. The counters are fully independent. The programmer can read the contents of any of the three counters without disturbing the actual count in process.

# **Operation Description**

The complete functional definition of the 8253 is programmed by the system software. Once programmed, the 8253 is ready to perform whatever timing tasks it is assigned to accomplish.

# Mode 0: Interrupt on terminal count

- 1. The output will be initially low after the mode set operation.

- 2. After the count is loaded into the selected count Register the output will remain low and the counter will count.

- 3. When the terminal count is reached the output will go high and remain high until the selected count is reloaded.

| D <sub>7</sub>  | •               | D <sub>5</sub>  | -               | <b>,</b>       | 4              |    | •   |

|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----|-----|

| SC <sub>1</sub> | SC <sub>0</sub> | RW <sub>1</sub> | RW <sub>0</sub> | M <sub>2</sub> | M <sub>1</sub> | Mo | BCD |

SC - Select counter

| SC1 | SC0 |                                                                          |

|-----|-----|--------------------------------------------------------------------------|

| 0   | 0   | Select counter 0                                                         |

| 0   | 1   | Select counter 1                                                         |

| 1   | 0   | Select counter 2                                                         |

| 1   | 1   | Illegal for 8253<br>Read -Back command for 8254<br>(See Read operations) |

| M - Mode |                |                |        |  |  |  |

|----------|----------------|----------------|--------|--|--|--|

| $M_2$    | M <sub>1</sub> | M <sub>0</sub> |        |  |  |  |

| 0        | 0              | 0              | Mode 0 |  |  |  |

| 0        | 0              | 1              | Mode 1 |  |  |  |

| x        | 1              | 0              | Mode 2 |  |  |  |

| x        | 1              | 1              | Mode 3 |  |  |  |

| 1        | 0              | 0              | Mode 4 |  |  |  |

| 1        | 0              | 1              | Mode 5 |  |  |  |

# RW - Read /Write

| 1.111 | 1.110 |                                                                       |   |   |                                                   |  |

|-------|-------|-----------------------------------------------------------------------|---|---|---------------------------------------------------|--|

| 0     | 0     | Counter latch command<br>(See Read operations)                        | в |   | SCD :                                             |  |

| 0     | 1     | Read / Write least significant byte only                              |   | 0 | Binary counter 16 - bits                          |  |

| 1     | 0     | Read / Write most significant byte only                               |   | 1 | Binary coded decimal (BCD)<br>Counter (4 Decades) |  |

| 1     | 1     | Read / write least significant byte first, then most significant byte |   |   | Counter (4 Decades)                               |  |

# Mode 1: Hardware Retriggerable One-shot

- 1. The output will be initially high

- 2. The output will go low on the CLK pulse following the rising edge at the gate input.

- 3. The output will go high on the terminal count and remain high until the next rising edge at the gate input.

# Mode 2: Rate generator

This mode functions like a divide by-N counter.

- 1. The output will be initially high.

- 2. The output will go low for one clock pulse before the terminal count.

- 3. The output then goes high, the counter reloads the initial count and the process is repeated.

- 4. The period from one output pulse to the next equals the number of input counts in the count register.

## Mode 3: Square wave mode

- 1. Initially output is high.

- 2. For even count, counter is decremented by 2 on the falling edge of each clock pulse. When the counter reaches terminal count, the state of the output is changed and the counter is reloaded with the full count and the whole process is repeated.

- 3. If the count is odd and the output is high the first clock pulse (after the count is loaded) decrements the count by 1. Subsequent clock pulses decrement the clock by 2. After timeout, the output goes low and the full count is reloaded. The first clock pulse decrements the count by 3 and subsequent clock pulse decrement the count by two. Then the whole process is repeated. In this way, if the count is odd, the output will be high for (n+1)/2 counts and low for (n-1)/2 counts.

# Mode 4: Software Triggered Strobe

- 1. The output will be initially high

- 2. The output will go low for one CLK pulse after the terminal count (TC).

# Mode 5: Hardware triggered strobe (Retriggerable)

- 1. The output will be initially high.

- 2. The counting is triggered by the rising edge of the Gate.

- 3. The output will go low for one CLK pulse after the terminal count (TC).

# **Programming the 8253**

Each counter of the 8253 is individually programmed by writing a control word into the control word register ( $A_0 - A_1 = 11$ ). The above figure shows the control word format. Bits SC<sub>1</sub> and SC<sub>0</sub> select the counter, bits RW<sub>1</sub> and RW<sub>0</sub> select the read, write or latch command, bits M<sub>2</sub>, M<sub>1</sub> and M<sub>0</sub> select the mode of operation and bit BCD decides whether it is a BCD counter or binary counter.

# **WRITE Operation**

- 1. Write a control word into control register.

- 2. Load the low-order byte of a count in the counter register.

- 3. Load the high-order byte of count in the counter register.

# **READ Operation**

In some applications, especially in event counters, it is necessary to read the value of the count in process. This can be done by following possible methods:

**Simple Read:** It involves reading a count after inhibiting the counter by controlling the gate input or the clock input of the selected counter, and two I/O read operations are performed by the CPU. The first I/O operation reads the low-order byte, and the second I/O operation reads the high order byte.

**Counter Latch Command:** In the second method, an appropriate control word is written into the control register to latch a count in the output latch, and two I/O read operations are performed by the CPU. The first I/O operation reads the low-order byte, and the second I/O operation reads the high order byte.

- Accepts IRQ, determines priority, checks whether incoming priority > current level being serviced, issues interrupt signal.

- In 8085 mode, provides 3-byte CALL instruction. In 8086 mode, provides 8-bit vector number.

24

• Polled and vectored mode.

- Starting address of ISR or vector number is programmable.

- No clock required.

# Pin Diagram

| ĈŜ   | 1  |      | 28 | Vcc   |

|------|----|------|----|-------|

| WR   | 2  |      | 27 | AD    |

| RD   | 3  |      | 26 | INTA  |

| D7   | 4  |      | 25 | IR7   |

| D6   | 5  |      | 24 | IR6   |

| D5   | 6  |      | 23 | IR5   |

| D4   | 7  | 8259 | 22 | IR4   |

| D3   | 8  | PIC  | 21 | IR3   |

| D2   | 9  |      | 20 | IR2   |

| D1   | 10 |      | 19 | IR1   |

| DO   | 11 |      | 18 | IRO   |

| CAS0 | 12 |      | 17 | INT   |

| CAS1 | 13 |      | 16 | SP/EN |

| gnd  | 14 |      | 15 | CAS2  |

# 8259 Pin Diagram

| $D_0-D_7$       | Bi-directional, tristate, buffered data lines. Connected to data                       |  |  |  |

|-----------------|----------------------------------------------------------------------------------------|--|--|--|

|                 | bus directly or through buffers                                                        |  |  |  |

| RD-bar          | Active low read control                                                                |  |  |  |

| WR-bar          | Active low write control                                                               |  |  |  |

| A0              | Address input line, used to select control register                                    |  |  |  |

| CS-bar          | Active low chip select                                                                 |  |  |  |

|                 | Bi-directional, 3-bit cascade lines. In master mode, PIC places slave ID no. on these  |  |  |  |

| CAS0-2          | lines. In slave mode, the PIC reads slave ID no. from master on these lines. It may be |  |  |  |

|                 | regarded as slave- select.                                                             |  |  |  |

| SP-bar / EN-bar | Slave program / enable. In non-buffered mode, it is SP-bar input, used to distinguish  |  |  |  |

|                 | master/slave PIC. In buffered mode, it is output line used to enable buffers           |  |  |  |

| INT             | VT Interrupt line, connected to INTR of microprocessor                                 |  |  |  |

| INTA-bar        | Interrupt ack, received active low from microprocessor                                 |  |  |  |

| IR0-7           | Asynchronous IRQ input lines, generated by peripherals.                                |  |  |  |

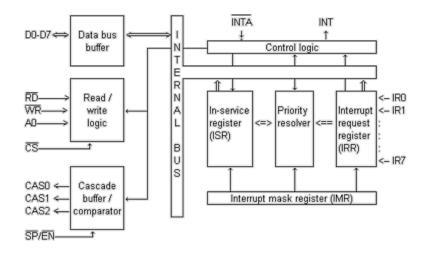

**Interrupt Request Register (IRR):** The interrupts at IRQ input lines are handled by Interrupt Request Register internally. IRR stores all the interrupt requests in it in order to serve them one by one on the priority basis.

**In-Service Register (ISR):** This register stores all the interrupt requests those are being served, i.e. ISR keeps a track of the requests being served.

**Priority Resolver:** This unit determines the priorities of the interrupt requests appearing simultaneously. The highest priority is selected and stored into the corresponding bit of ISR during

INTA pulse. The IRO has the highest priority while the IR7 has the lowest one, normally in fixed priority mode. The priorities however may be altered by programming the 8259A in rotating priority mode.

**Interrupt Mask Register (IMR):** This register stores the bits required to mask the interrupt puts. IMR operates on IRR at the direction of the Priority Resolver.

**Interrupt Control Logic:** This block manages the interrupt and interrupt acknowledge signals to be sent to the CPU for serving one of the eight interrupt requests. This also accepts interrupt acknowledge (INTA) signal from CPU that causes the 8259A to release vector address on to the data bus.

**Data Bus Buffer:** This tristate bidirectional buffer interfaces internal 8259A bus to the microprocessor system data bus. Control words, status and vector information pass through buffer during read or write operations.

**Read write Control Logic:** This circuit accepts and decodes commands from the CPU. This also allows the status of the 8259A to be transferred on to the data bus.

**Cascade Buffer/Comparator:** This block stores and compares the ID's of all the 8259As used in the system. The three I/O pins CAS0-2 are outputs, when the 8259A is used as a master. The same pins act as inputs when the 8259A is in slave mode. The 8259A in master mode sends the ID of the interrupting slave device on these lines. The slave thus selected, will send its pre-programmed vector address on the data bus during the next INTA pulse.

# **Interrupt Sequence**

The powerful features of the 8259A in a microcomputer system are its programmability and the interrupt routine addressing capability. The latter allows direct or indirect jumping to the specific interrupt routine requested without any polling of the interrupting devices. The normal sequence of events during an interrupt depends on the type of CPU being used. The events occur as follows in an 8085 system:

- 1. One or more of the INTERRUPT REQUEST lines (IR7–0) are raised high, setting the corresponding IRR bit(s).

- 2. The 8259A evaluates these requests, and sends an INT to the CPU, if appropriate.

- 3. The CPU acknowledges the INT and responds with an INTA pulse.

- 4. Upon receiving an INTA from the CPU group, the highest priority ISR bit is set, and the corresponding IRR bit is reset. The 8259A will also release a CALL instruction code (11001101) onto the 8-bit Data Bus through its D7–0 pins.

- 5. This CALL instruction will initiate two more INTA pulses to be sent to the 8259A from the CPU group.

- 6. These two INTA pulses allow the 8259A to release its preprogrammed subroutine address onto the Data Bus. The lower 8-bit address is released at the first INTA pulse and the higher 8-bit address is released at the second INTA pulse.

- 7. This completes the 3-byte CALL instruction released by the 8259A. In the AEOI mode the ISR bit is reset at the end of the third INTA pulse.

- 8. Otherwise, the ISR bit remains set until an appropriate EOI command is issued at the end of the interrupt sequence.

When the 8259A PIC receives an interrupt, INT becomes active and an interrupt acknowledge cycle is started. If a higher priority interrupt occurs between the two INTA pulses, the INT line goes inactive immediately after the second INTA pulse. After an unspecified amount of time the INT line is activated again to signify the higher priority interrupt waiting for service. This inactive time is not specified and can vary between parts.

#### Seven Segment display Interface

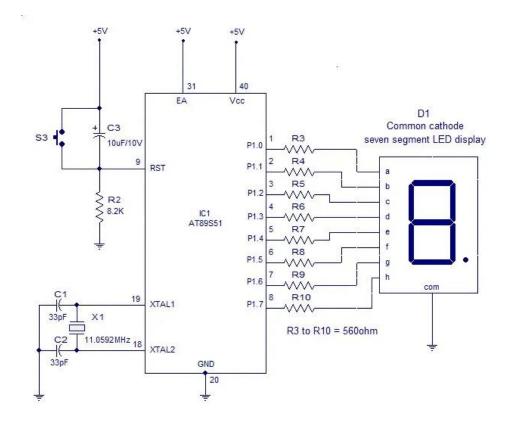

A seven-segment display to 8085 to display alphabet, number, signs or symbols e.t.c., Even the programming aspect of it which is done with assembly language will also be shown. But before we continue what is a microcontroller? microcontroller is a small computer on a single metal-oxide-semiconductor (MOS) integrated circuit (IC) chip or A microcontroller is an integrated circuit (IC) device used for controlling other portions of an electronic system, usually via a microprocessor unit (MPU), memory, and some peripherals. It has 40 pinout the name or functions of the pins are labelled on the picture below.

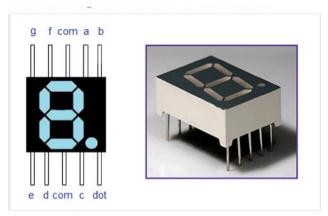

A seven-segment display is the most basic electronic display device that can display digits from 0–9. The most common configuration has an array of eight LEDs arranged in a special pattern to display these digits. They are laid out as a squared-off figure. Seven segment displays are of two types, common cathode and common anode. In common cathode type , the cathode of all LEDs are tied together to a single terminal and the anode of all LEDs are left alone as individual pins labeled as a, b, c, d, e, f, g & h (for dot). In common anode type, the anode of all LEDs are tied together as a single terminal and cathodes are left alone as individual pins. It will take a high (1) to turn a LED ON in common cathode and will take a low (0) to turn a LED ON in a common anode seven segment display.

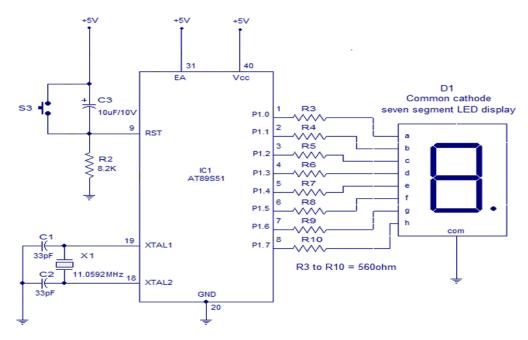

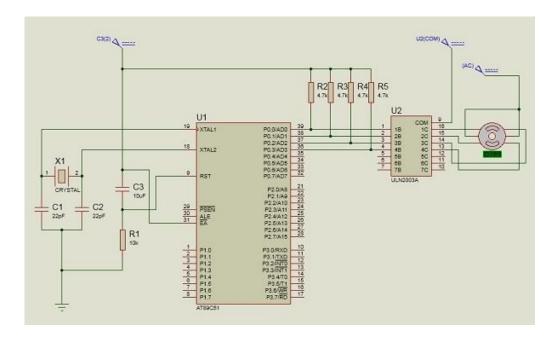

The circuit diagram shown below is of an AT89S51 microcontroller based 0 to 9 counter which has a 7 segment LED display interfaced to it in order to display the count. This simple circuit illustrates two things. How to setup simple 0 to 9 up counter using 8051 and more importantly how to interface a seven segment LED display to 8051 in order to display a particular result. The common cathode seven segment display D1 is connected to the Port 1 of the microcontroller (AT89S51) as shown in the circuit diagram. R3 to R10 are current limiting resistors. S3 is the reset switch and R2,C3 forms a debouncing circuitry. C1, C2 and X1 are related to the clock circuit. The software part of the project has to do the following tasks.

Form a 0 to 9 counter with a predetermined delay (around 1/2 second here).

Convert the current count into digit drive pattern.

Put the current digit drive pattern into a port for displaying.

# All the above said tasks are accomplished by the program given below.

## Program.

ORG 000H //initial starting address

START: MOV A, #00001001B // initial value of accumulator

MOV B, A

MOV R0, #0AH //Register R0 initialized as counter which counts from 10 to 0

29

LABEL: MOV A, B

INC A MOV B, A MOVC A, @A+PC // adds the byte in A to the program counters address MOV P1, A ACALL DELAY // calls the delay of the timer DEC R0//Counter R0 decremented by 1 MOV A, R0 // R0 moved to accumulator to check if it is zero in next instruction. JZ START //Checks accu

# ADC and DAC Interfacing:

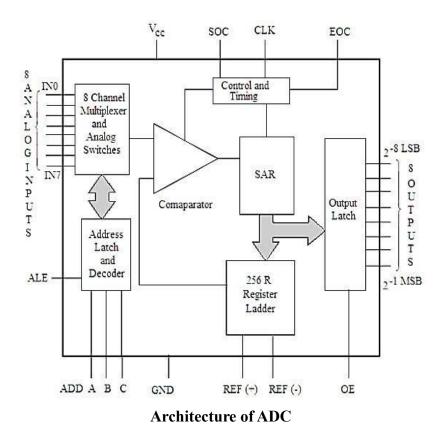

The Analog to Digital Conversion is a quantizing process. Here the analog signal is represented by equivalent binary states. The A/D converters can be classified into two groups based on their conversion techniques.

In the first technique it compares given analog signal with the initially generated equivalent signal. In this technique, it includes successive approximation, counter and flash type converters. In another technique it determines the changing of analog signals into time or frequency. This process includes integrator-converters and voltage-to- frequency converters. The first process is faster but less accurate, the second one is more accurate. As the first process uses flash type, so it is expensive and difficult to design for high accuracy.

## ADC 0808/0809 Chip

The ADC 0808/0809 is an 8-bit analog to digital converter. It has 8 channel multiplexers to interface with the microprocessor.

This chip is popular and widely used ADC. ADC 0808/0809 is a monolithic CMOS device. This device uses successive approximation technique to convert analog signal to digital form. One of the main advantages of this chip is that it does not require any external zero and full scale adjustment, only +5V DC supply is sufficient.

Let us see some good features of ADC 0808/0809:

- The conversion speed is much higher

- The accuracy is also high

- It has minimal temperature dependence

- Excellent long-term accuracy and repeatability

- Less power consumption

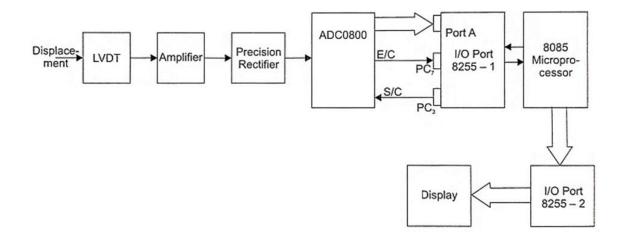

[Source: "Microprocessor Architecture Programming and Application" by R.S. Gaonkar, page-] Interfacing ADC with 8085 Microprocessor

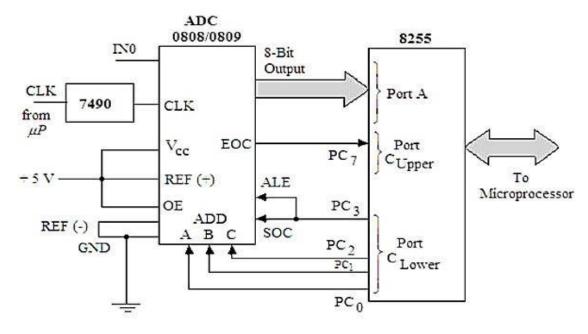

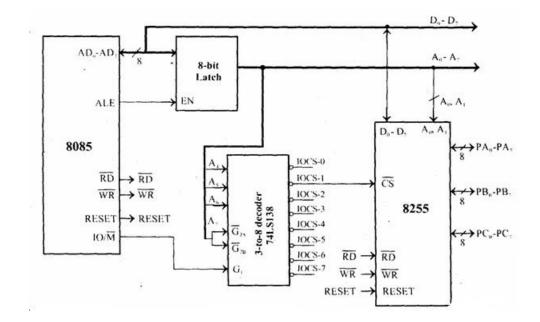

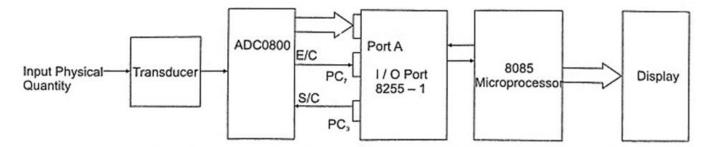

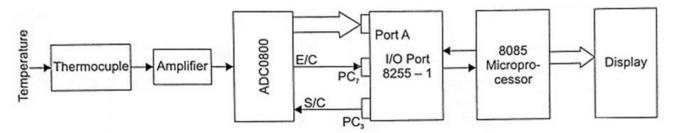

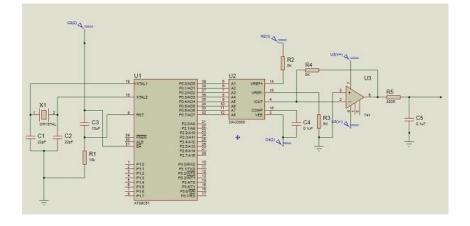

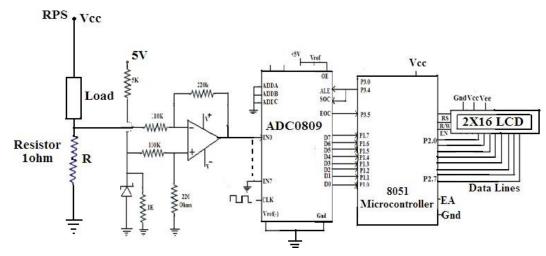

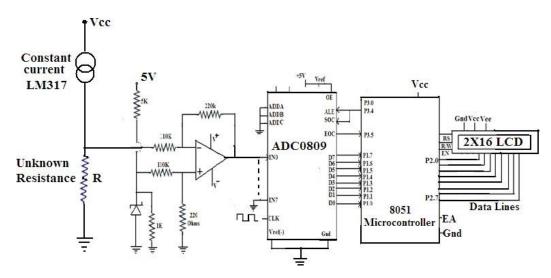

To interface the ADC with 8085, we need 8255 Programmable Peripheral Interface chip with it. Let us see the circuit diagram of connecting 8085, 8255 and the ADC converter.

Interfacing ADC with 8085 Microprocessor

# [Source: "Microprocessor Architecture Programming and Application" by R.S. Gaonkar]

The Port A of 8255 chip is used as the input port. The PC7 pin of Port Cupper is connected to the End of Conversion (EOC) Pin of the analog to digital converter. This port is also used as input port. The Clower port is used as output port. The PC2-0 lines are connected to three address pins of this chip to select input channels. The PC3 pin is connected to the Start of Conversion (SOC) pin and ALE pin of ADC 0808/0809.

Now let us see a program to generate digital signal from analog data. We are using IN0 as input pin, so the pin selection value will be 00H.

MVI A, 98H; Set Port A and Cupper as input, C Lower as output OUT 03H; Write control word 8255-I to control Word register XRA A; Clear the accumulator OUT 02 H; Send the content of Acc to Port Clower to select IN0 MVI A, 08H; Load the accumulator with 08H OUT 02H ; ALE and SOC will be 0 XRA A; Clear the accumulator OUT 02H; ALE and SOC will be low. READ: IN 02H ; Read from EOC (PC7) RAL; Rotate left to check C7 is 1. JNC READ; If C7 is not 1, go to READ IN 00H ; Read digital output of ADC STA 8000H ; Save result at 8000H HLT; Stop the program

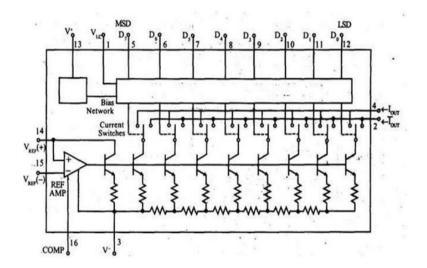

# **DAC Interfacing with 8085 Microprocessor**

- DAC 0800 Features

- To convert the digital signal to analog signal a Digital-to-Analog Converter (DAC) has to be employed.

- The DAC will accept a digital (binary) input and convert to analog voltage or current.

- Every DAC will have "n" input lines and an analog output.

- The DAC require a reference analog voltage (Vref) or current (Iref) source.

- The smallest possible analog value that can be represented by the n-bit binary code is called resolution.

- The resolution of DAC with n-bit binary input is 1/2nof reference analog value.

- The DAC0800 is an 8-bit, high speed, current output DAC with a typical settling time (conversion time) of 100 ns.

- It produces complementary current output, which can be converted to voltage by using simple resistor load.

- The DAC0800 require a positive and a negative supply voltage in the range of ± 5V to ±18V.

*Circuit Diagram of 0800* [Source: "Microprocessor Architecture Programming and Application" by R.S. Gaonkar]

- It can be directly interfaced with TTL, CMOS, PMOS and other logic families.

- For TTL input, the threshold pin should be tied to ground (VLC = 0V).

- The reference voltage and the digital input will decide the analog output current, which can be converted to a voltage by simply connecting a resistor to output terminal or by using an op-amp I to V converter.

- The DAC0800 is available as a 16-pin IC in DIP.

# Stepper motor Interfacing/Control using 8085 and 8051

# **Stepper Motor**

A stepper motor is a device that translates electrical pulses into mechanical movement in steps of fixed step angle.

- The stepper motor rotates in steps in response to the applied signals.

- It is mainly used for position control.

• It is used in disk drives, dot matrix printers, plotters and robotics and process control circuits.

| ADDRESS | LABEL | MNEMONICS    | OPCODE |

|---------|-------|--------------|--------|

|         | START | MVIA,00H     |        |

|         |       | OUT C8       |        |

|         |       | CALL DISPLAY |        |

|         |       | MVI A,FF     |        |

|         |       | OUT C8       |        |

|         |       | CALL DELAY   |        |

|         |       | JMP START    |        |

|         |       | MVI B,05H    |        |

|         |       | MVI C,FF     |        |

|         | DELAY | DCR C        |        |

|         | L2    | JNZ L1       |        |

|         |       | DCR C        |        |

|         |       | JNZ L1       |        |

|         |       | DCR B        |        |

|         | L1    | JNL L2       |        |

|         |       | RET          |        |

#### **Square Wave Generation Using DAC 0800:**

#### Structure

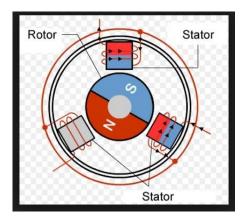

Stepper motors have a permanent magnet called rotor (also called the shaft) surrounded by a stator. The most common stepper motors have four stator windings that are paired with a center-tap. This type of stepper motor is commonly referred to as a four-phase or unipolar stepper motor. The center tap allows a change of current direction in each of two coils when a winding is grounded, thereby resulting in a polarity change of the stator.

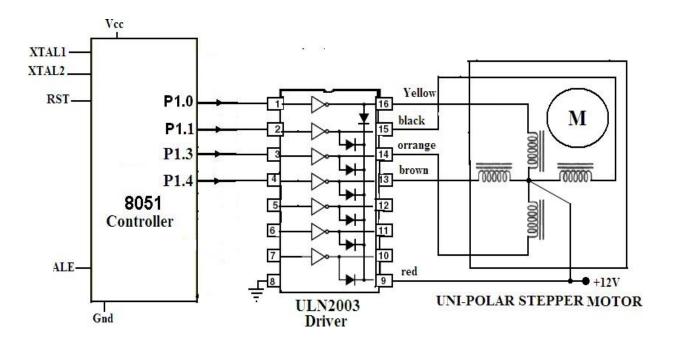

#### Interfacing

Even a small stepper motor requires a current of 400 mA for its operation. But the ports of the microcontroller cannot source this much amount of current. If such a motor is directly connected to the microprocessor/microcontroller ports, the motor may draw large current from the ports and damage it. So, a suitable driver circuit is used with the microprocessor/microcontroller to operate the motor.

### **Motor Driver Circuit (ULN2003)**

Stepper motor driver circuits are available readily in the form of ICs. ULN2003 is one such driver IC which is a High-Voltage High-Current Darlington transistor array and can give a current of 500mA. This current is sufficient to drive a small stepper motor. Internally, it has protection diodes used

to protect the motor from damage due to back emf and large eddy currents. So, this ULN2003 is used as a driver to interface the stepper motor to the microcontroller.

## Operation

The important parameter of a stepper motor is the step angle. It is the minimum angle through which the motor rotates in response to each excitation pulse. In a four-phase motor if there are 200 steps in one complete rotation then the step angle is  $360/200 = 1.8^{\circ}$ . So, to rotate the stepper motor we have to apply the excitation pulse. For this the controller should send a hexa decimal code through one of its ports. The hex code mainly depends on the construction of the stepper motor. So, all the stepper motors do not have the same Hex code for their rotation.

For example, let us consider the hex code for a stepper motor to rotate in clockwise direction is 77H, BBH, DDH and EEH. This hex code will be applied to the input terminals of the driver through the assembly language program. To rotate the stepper motor in anti-clockwise direction the same code is applied in the reverse order.

## **Stepper Motor interface- Schematic Diagram (for 8051)**

The assembly language program for 8051 is given below.

## ASSEMBLY LANGUAGE PROGRAM (8051)

| Main | : MOV A, # 0FF H | ; Initialization of Port 1 |

|------|------------------|----------------------------|

|      | MOV P1, A        | ;                          |

|      | MOV A, #77 H     | ; Code for the Phase 1     |

|      | MOV P1, A        | ;                          |

|      | ACALL DELAY      | ; Delay subroutine         |

|      | MOV A, # BB H    | ; Code for the Phase II    |

|      | MOV P1, A        | ;                          |

|      | ACALL DELAY      | ; Delay subroutine.        |

|      | MOV A, # DD H    | ; Code for the Phase III   |

|      | MOV P1, A        | ;                          |

|      | ACALL DELAY      | ; Delay subroutine         |

|      | MOV A, # EE H    | ; Code for the Phase 1     |

|      | MOV P1, A        | ;                          |

|      | ACALL DELAY      | ; Delay subroutine SJMP    |

|      |                  |                            |

MAIN; Keep the motor rotating continuously.

## DELAY Subroutine

| MOV R4, #0FF H        | ; Load R4 with FF                      |

|-----------------------|----------------------------------------|

| MOV R5, # 0FF         | ; Load R5 with FF                      |

| LOOP1: DJNZ R4, LOOP1 | ; Decrement R4 until zero, wait LOOP2: |

| DJNZ R5, LOOP2        | ; Decrement R5 until zero, wait        |

| RET                   | ; Return to main program               |

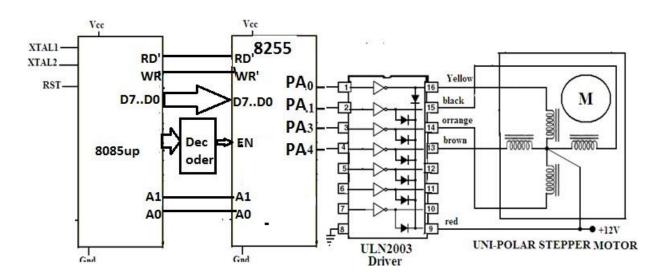

**Stepper Motor interface - Schematic Diagram for (8085)**

# Detailed Connection diagram between 8085 and 8255

# **ASSEMBLY LANGUAGE PROGRAM (8085)**

| Main | : MVI A, 80             | ; $80H \rightarrow Control \text{ word to configure PA,PB,PC in O/P}$ |

|------|-------------------------|-----------------------------------------------------------------------|

|      | OUT CWR_Address         | ; Write control word in CWR of 8255                                   |

|      | MVI A, 77               | ; Code for the Phase 1                                                |

|      | OUT PortA_Address       | ; sent to motor via port A of 8255 ;                                  |

|      | CALL DELAY              | ; Delay subroutine                                                    |

|      | MVI A, BB               | ; Code for the Phase II                                               |

|      | OUT PortA_Address       | ; sent to motor via port A of 8255                                    |

|      | CALL DELAY              | ; Delay subroutine.                                                   |

|      | MVI A, DD               | ; Code for the Phase III                                              |

|      | OUT PortA_Address       | ; sent to motor via port A of 8255;                                   |

|      | CALL DELAY              | ; Delay subroutine                                                    |

|      | MVI A, EE H             | ; Code for the Phase 1                                                |

|      | OUT PortA_Address       | ; sent to motor via port A of 8255 ;                                  |

|      | CALL DELAY              | ; Delay subroutine                                                    |

|      | JMP MAIN                | ; Keep the motor rotating continuously.                               |

|      | <b>DELAY Subroutine</b> |                                                                       |

|      | MVI C, FF               | ; Load C with FF Change it for the speed variation LOOP1:             |

|      | MVI D,FF                | ; Load D with FF                                                      |

|      | LOOP2: DCR D            |                                                                       |

|      | JNZ LOOP2 DCR C         |                                                                       |

|      |                         |                                                                       |

JNZ LOOP1

RET

; Return to main program .

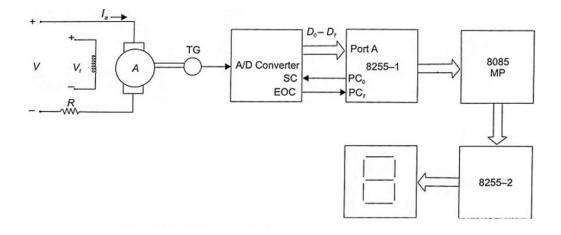

### **Basic electrical quantities**

The basic electrical quantities are electrical current and voltage, electrical charge, resistance, capacitance, inductance and electric power. Electricity is a flow of free electrons carrying negative electric charge from the place with their excess (place with negative charge) to the place with their deficiency (place with positive charge). 2.1. Electrical current and charge According the convention, the positive direction of electric current is opposite, i.e. the positive direction of electric current is from the place with positive charge to the place with negative charge. The symbol for electric current is I (or i if the current is time varying) and the basic unit of measure is ampere (symbol A) after André-Marie Ampère. The ampere is one of seven basic units according to international convention (SI), which definition is: "the ampere is that constant current which, if maintained in two straight parallel conductors of infinite length, of negligible circular cross-section, and placed 1 meter apart in vacuum, would produce between these conductors a force equal to  $2 \times 10^{-7}$  newton per meter of length". Another simpler definition comes from the fact that electric current is movement of elementary electric charges carried by electrons. When there is a constant flow of approximately  $1.602176487 \times 10^{19}$  electrons per second trough a surface, the current of 1 amper is flowing.

The unit of measure charge is coulomb (symbol C) after Charles Augustin de Coulomb. One coulomb is approximately 1.602176487×1019 of elementary charges. The SI definition of coulomb is "the coulomb is the quantity of electricity carried in 1 second by a current of 1 ampere". Although electrical charge is one of basic electrical quantities it is measured very rarely in praxis and if needed usually only calculated from measurement of other electrical quantities.

**Electrical voltage** Electrical voltage is a difference of potential between two places with different charges. Voltage provides the ability to move charges and hence: do a work and therefore voltage is also sometimes called electromotive force (EMF). The symbol for voltage is V or sometimes U (v or u if the voltage is time varying quantities) and the unit of measure is volt (V) after Alessandro Volta. The SI definition is: "The volt is the potential difference between two points of a conducting wire carrying a constant current of 1 ampere, when the power dissipated between these points is equal to 1 watt". Electrical voltage and current are manifestation of electrical charge movement and the can be supposed to be "active" quantities. They can carry information in electronic circuits and systems or they can be supposed to be only expression of supplied and consumed electrical energy. Measurement methods and instrumentation as well as measured parameters differ from a point of view where and why the voltage and current are measured.

## **Measurement of Physical Quantities:**

Measurement of Physical Quantities is given by

- Displacement Measurement

- Strain Measurement

- Force Measurement

- Torque Measurement

- Pressure Measurement

- Temperature Measurement

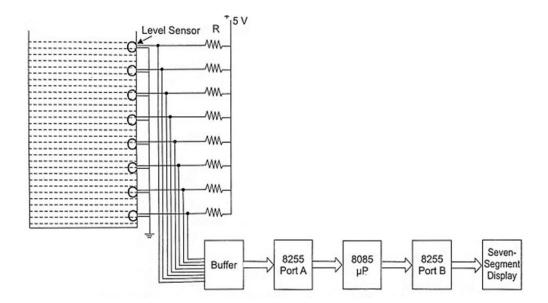

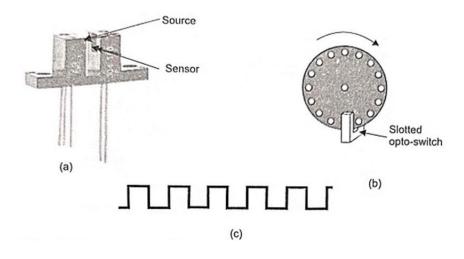

- Water-Level Indicator

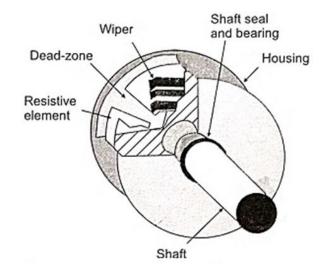

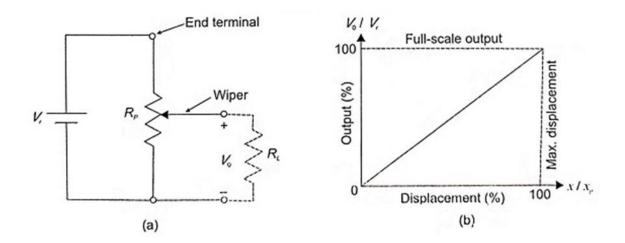

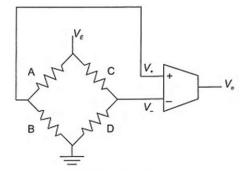

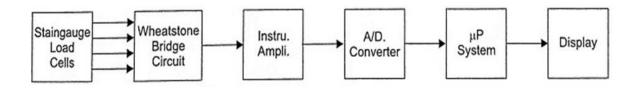

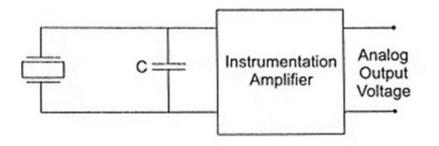

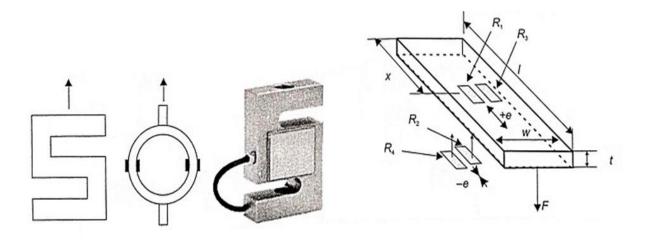

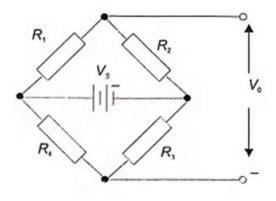

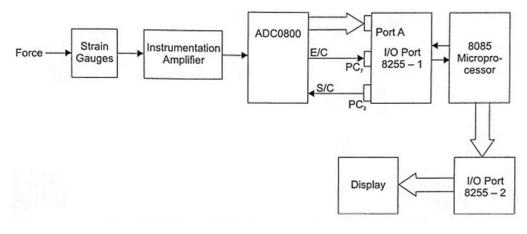

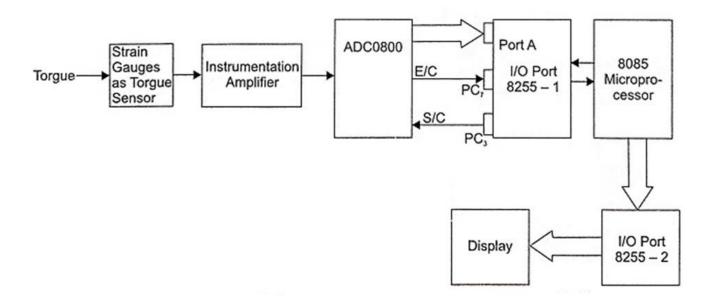

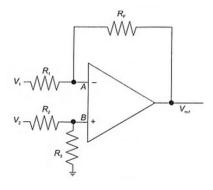

- Measurement and Display of Speed of a Motor